## Attacking and Protecting Constrained Embedded Systems from Control Flow Attacks

Aurélien Francillon

## ▶ To cite this version:

Aurélien Francillon. Attacking and Protecting Constrained Embedded Systems from Control Flow Attacks. Networking and Internet Architecture [cs.NI]. Institut National Polytechnique de Grenoble - INPG, 2009. English. NNT: . tel-00540371

## HAL Id: tel-00540371 https://theses.hal.science/tel-00540371v1

Submitted on 26 Nov 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## INSTITUT POLYTECHNIQUE DE GRENOBLE

| $N^{\circ}$ | attr | ribu | é p | ar i | la b | oibl | ioth | ièqi | ue |

|-------------|------|------|-----|------|------|------|------|------|----|

|             |      |      |     |      |      |      |      |      |    |

## THÈSE

pour obtenir le grade de

#### **DOCTEUR de l'Institut Polytechnique de Grenoble**

Spécialité : Informatique

préparée a l'**INRIA Rhône-Alpes, Projet Planète**

dans le cadre de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

présentée et soutenue publiquement par

## **Aurélien Francillon**

le 7 Octobre 2009

## Attacking and Protecting Constrained Embedded Systems from Control Flow Attacks

Directeur de thèse: Claude Castelluccia

| Jury                     |                    |

|--------------------------|--------------------|

| Pr. Andrzej Duda,        | Président du jury  |

| Pr. Jean-Louis Lanet,    | Rapporteur         |

| Pr. Peter Langendörfer,  | Rapporteur         |

| Pr. Levente Buttyán,     | Membre du jury     |

| Pr. Éric Filiol,         | Membre du jury     |

| Dr. Claude Castelluccia, | Directeur de thèse |

## Résumé

La sécurité des systèmes embarqués très contraints est un domaine qui prend de l'importance car ceux-ci ont tendance à être toujours plus connectés et présents dans de nombreuses applications industrielles aussi bien que dans la vie de tous les jours. Cette thèse étudie les attaques logicielles dans le contexte des systèmes embarqués communicants par exemple de type réseaux de capteurs. Ceux-ci, reposent sur diverses architectures qui possèdent souvent, pour des raisons des coût, des capacités de calcul et de mémoire très réduites. Dans la première partie de cette thèse nous montrons la faisabilité de l'injection de code dans des micro-contrôleurs d'architecture Harvard, ce qui était, jusqu'à présent, souvent considéré comme impossible. Dans la seconde partie nous étudions les protocoles d'attestation de code. Ceux-ci permettent de détecter les équipements compromis dans un réseau de capteurs. Nous présentons plusieurs attaques sur les protocoles d'attestation de code existants. De plus nous proposons une méthode améliorée permettant d'éviter ces attaques. Finalement, dans la dernière partie de cette thèse, nous proposons une modification de l'architecture mémoire d'un micro-contrôleur. Cette modification permet de prévenir les attaques de manipulation du flot de contrôle, tout en restant très simple a implémenter.

## Abstract

The security of low-end embedded systems became a very important topic as they are more connected and pervasive. This thesis explores software attacks in the context of embedded systems such as wireless sensor networks. These devices usually employ a micro-controller with very limited computing capabilities and memory availability, and a large variety of architectures. In the first part of this thesis we show the possibility of code injection attacks on Harvard architecture devices, which was largely believed to be infeasible. In the second part we describe attacks on existing software-based attestation techniques. These techniques are used to detect compromises of WSN Nodes. We propose a new method for software-based attestation that is immune of the vulnerabilities in previous protocols. Finally, in the last part of this thesis we present a hardware-based technique that modifies the memory layout to prevent control flow attacks, and has a very low overhead.

## Foreword

This manuscript presents some of the work performed during my PhD at INRIA Rhone-Alpes in the Planète Team. It is mainly based on the work that has been published in the papers [FC08, CFPS09, FPC09], for whom I am the main author. A complete list of publications is given below.

Some of the techniques presented in this document, either already existing (State of the art section) or new attacks we present, can be used for malicious purpose. We strongly disregard any illegal activities that could be performed using the techniques described here. On the other hand we believe that better public knowledge of such techniques will help the community to develop proper defenses.

The work presented in this thesis was supported in part by the European Commission within the STREP UbiSec&Sens project. The views and conclusions contained herein are those of the authors and should not be interpreted as representing the official policies or endorsement of the UbiSec&Sens project or the European Commission. No motes were harmed during the making of this thesis except one who genuinely deserved it.

## Published work during the PhD

#### **INTERNATIONAL CONFERENCES**

- [CFPS09] Claude Castelluccia, Aurélien Francillon, Daniele Perito and Claudio Soriente. On the Difficulty of Software-Based Attestation of Embedded Devices. In CCS'09: Proceedings of the 16th ACM conference on Computer and Communications Security, November 2009. ACM.

- [FC08] Aurélien Francillon and Claude Castelluccia. Code injection attacks on Harvardarchitecture devices. In CCS '08: Proceedings of the 15th ACM conference on Computer and Communications Security, October 2008. ACM.

- [FC07] Aurélien Francillon and Claude Castelluccia. *TinyRNG: A Cryptographic Random Number Generator for Wireless Sensors Network Nodes*. In WiOpt 07: Proceedings of the 5th International Symposium on Modeling and Optimization in Mobile, Ad Hoc and Wireless Networks, April 2007.

#### **INTERNATIONAL WORKSHOPS**

[FPC09] Aurélien Francillon, Daniele Perito, and Claude Castelluccia. *Defending Embedded Systems Against Control Flow Attacks*. In Sven Lachmund and Christian Schaefer editors, 1st ACM workshop on secure code execution, SecuCode'09, ACM, 2009.

[GF09] Travis Goodspeed and Aurélien Francillon. Half-blind attacks: Mask ROM Bootloaders are Dangerous. In Dan Boneh and Alexander Sotirov, editors, WOOT '09, 3rd USENIX Workshop on Offensive Technologies. USENIX Association, 2009.

#### **OTHERS**

- [CF08] Claude Castelluccia and Aurélien Francillon. *Sécurité dans les réseaux de capteurs (invited paper).* In SSTIC 08 Symposium sur la Sécurité des Technologies de l'Information et des Communications 2008, Rennes, France, June 2008.

- [Fra07] Aurélien Francillon. Roadsec&sens : Réseaux de capteurs sécurisés, application à la sécurité routière. Demo at XIVes Rencontres INRIA - Industrie Confiance et Sécurité, Octobre 2007.

## Acknowledgments

Firstly, I would like to thank the jury members: Prof Andrzej Duda from INPG, Prof. Jean-Louis Lanet from university of Limoges, Prof. Peter Langendörfer of IHP Microelectronics, Prof. Levente Buttyán of Budapest University of Technology and Economics and Éric Filiol from ESIEA. It is a great honor for that they accepted to be in my jury.

I would like to specifically thank Jean-Louis Lanet and Peter Langendörfer who kindly accepted to review this manuscript. Their invaluable comments were greatly appreciated.

I sincerely thank my adviser, Claude Castelluccia, without whom this work would not have been possible. I'm specially grateful for the great work environment he provides for a PhD with a great balance between directions and freedom in research topics.

I'm also specially indebted to Vincent Roca who gave me the desire to pursue the a PhD, working with him prior to PhD was a great experience.

I feel lucky to have worked with amazing co-authors an I'm sincerely thankful to them: Claude, Vincent, Claudio, Travis and Daniele.

All the current or former colleagues at INRIA that were either supportive, helpful or coffee breaks mates: Dali Kaafar, José Khan, Mathieu Cunche, Nitesh Saxena, Christoph Neumann, Nabil Layaïda, Angelo Spognardi, Maté Soos, Lionel Giraud, Pars Mutaf as well as friends and colleagues from other places Hugo Venturini, Michael Hertel, and the ones I forgot to mention!

I would like to thank people at INRIA's SED team and more specifically Gerard Baille, Roger Pissard-Gibolet, Christoph Braillon for their kind help with electronics and related issues as well as the fruitful discussions.

I would like to sincerely thank Yves Perret of "Cuisine et Réceptions à Domicile" for the reception that took place after the defense, this was greatly appreciated !

Last but not least my family, for their amazing support and presence. I am especially dedicating this thesis to the ones who arrived and the ones who left during this PhD.

## Contents

| Ré | ésumé  |          |              |                                                        | 3  |

|----|--------|----------|--------------|--------------------------------------------------------|----|

| Al | ostrac |          |              |                                                        | 4  |

|    | Ack    | nowledg  | gments       |                                                        | 7  |

| 1  | Intr   | oductio  | n            |                                                        | 17 |

|    | 1.1    | Contex   | t of this w  | vork                                                   | 17 |

|    |        | 1.1.1    | Constrai     | ned embedded systems                                   | 17 |

|    |        | 1.1.2    | Wireless     | Sensor Networks                                        | 18 |

|    |        | 1.1.3    | Embedde      | ed systems security                                    | 19 |

|    | 1.2    | Proble   | m Stateme    | ent                                                    | 19 |

|    |        | 1.2.1    | Overview     | w of possible attacks                                  | 20 |

|    |        | 1.2.2    | Software     | e attacks                                              | 21 |

|    | 1.3    | Contri   | butions .    |                                                        | 21 |

|    | 1.4    | Organi   | isation of t | the thesis                                             | 22 |

| 2  | Stat   | e of The | e Art        |                                                        | 23 |

|    | 2.1    | Overvi   | iew of con   | nmon WSN device architectures                          | 23 |

|    |        | 2.1.1    | Harvard      | architecture: the AVR                                  | 23 |

|    |        |          | 2.1.1.1      | The AVR architecture                                   | 24 |

|    |        |          | 2.1.1.2      | Memory architecture                                    | 24 |

|    |        |          | 2.1.1.3      | The bootloader                                         | 25 |

|    |        |          | 2.1.1.4      | Wireless Sensor Nodes based on the AVR architecture .  | 26 |

|    |        | 2.1.2    | Von Neu      | mann architecture: TI MSP430                           | 26 |

|    |        |          | 2.1.2.1      | The MSP430 architecture                                | 26 |

|    |        |          | 2.1.2.2      | Memory architecture                                    | 27 |

|    |        |          | 2.1.2.3      | The Bootloader                                         | 27 |

|    |        |          | 2.1.2.4      | Wireless Sensor Nodes based on the MSP430 architecture | 27 |

|    | 2.2    | Softwa   | are attacks  | and counter-measures on general purpose computers      | 28 |

|    |        | 2.2.1    | Software     | e attacks on general purpose computers                 | 28 |

|    |        |          | 2.2.1.1      | Code injection attacks                                 | 28 |

|    |        |          | 2.2.1.2      | Malicious code execution without code injection        | 31 |

|    |        |          | 2.2.1.3      | Non buffer overflow-based software attacks             | 32 |

|    |        | 2.2.2    | Mitigatio    | on techniques on general purpose computers             | 33 |

|    |        |          | 2.2.2.1      | Preventive measures                                    | 33 |

|    |        |          | 2.2.2.2      | Protecting the stack                                   | 34 |

|    |        |          | 2.2.2.3      | Making exploitation of control flow attacks difficult  | 35 |

|    |        |          | 2.2.2.4      | Protection by modification of the stack model          | 36 |

|   |                 |           | 2.2.2.5 Malicious code detection                              | 37        |

|---|-----------------|-----------|---------------------------------------------------------------|-----------|

|   | 2.3             | Softwa    | are attacks and detection on WSN nodes                        | 37        |

|   |                 | 2.3.1     | Attacks                                                       | 37        |

|   |                 |           | 2.3.1.1 Stack execution on Von Neumann architecture sensors . | 38        |

|   |                 |           |                                                               | 38        |

|   |                 |           |                                                               | 38        |

|   |                 | 2.3.2     |                                                               | 40        |

|   |                 |           |                                                               | 41        |

|   |                 |           | 8 1 1                                                         | 41        |

|   | 2.4             | Conclu    | 81 1                                                          | 43        |

| _ | • • • •         | . ~       |                                                               |           |

| 3 | <b>Atta</b> 3.1 |           | <b>J</b>                                                      | <b>45</b> |

|   |                 |           |                                                               | 45        |

|   | 3.2             |           |                                                               | 40<br>46  |

|   |                 | 3.2.1     | I                                                             | -         |

|   |                 |           | I I I I I I I I I I I I I I I I I I I                         | 47        |

|   | 2.2             | т         |                                                               | 47        |

|   | 3.3             |           | I I I I I I I I I I I I I I I I I I I                         | 49        |

|   |                 | 3.3.1     | J. B.                     | 49        |

|   |                 | 3.3.2     | J. B. I.                  | 49        |

|   |                 | 3.3.3     |                                                               | 50        |

|   | 3.4             | -         |                                                               | 51        |

|   |                 | 3.4.1     | 1                                                             | 51        |

|   |                 | 3.4.2     |                                                               | 53        |

|   |                 |           | J 0 0                                                         | 53        |

|   |                 |           |                                                               | 54        |

|   |                 |           |                                                               | 54        |

|   |                 | 3.4.3     | 6 5 6                                                         | 56        |

|   |                 |           | 8                                                             | 57        |

|   |                 |           | J 8                                                           | 57        |

|   |                 | 3.4.4     | Flashing the malware into program memory                      | 57        |

|   |                 | 3.4.5     | Finalizing the malware installation                           | 59        |

|   |                 | 3.4.6     | Turning the malware into a worm                               | 59        |

|   | 3.5             | Possib    | le Counter-measures                                           | 60        |

|   |                 | 3.5.1     | Software vulnerability Protection                             | 60        |

|   |                 | 3.5.2     | Stack-smashing protection                                     | 60        |

|   |                 | 3.5.3     | Data injection protection                                     | 60        |

|   |                 | 3.5.4     | Gadget execution protection                                   | 61        |

|   | 3.6             | Conclu    | usions and future work                                        | 61        |

| 4 | Dete            | ection: S | Software-Based Attestation                                    | 63        |

| • | 4.1             |           |                                                               | 64        |

|   | 4.2             |           |                                                               | 64        |

|   | 4.3             |           | <b>I</b>                                                      | 66        |

|   |                 | 4.3.1     | -                                                             | 66        |

|   |                 | 1.2.1     |                                                               | 66        |

|   |                 |           | 1                                                             | 67        |

|   |                 |           | L                                                             | 69        |

|   |                 |           |                                                               | 07        |

|   |      |          | 4.3.1.4 D      | Discussion                                       | 69       |

|---|------|----------|----------------|--------------------------------------------------|----------|

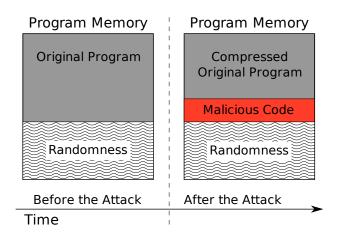

|   |      | 4.3.2    | Compressio     | on attack                                        | 69       |

|   |      |          | 4.3.2.1 II     | mplementation Details                            | 70       |

|   | 4.4  | On the   |                | -                                                | 71       |

|   |      | 4.4.1    | •              |                                                  | 71       |

|   |      |          |                |                                                  | 71       |

|   |      |          |                | 5 6                                              | 72       |

|   |      |          |                |                                                  | 74       |

|   |      | 4.4.2    |                | 8                                                | 74       |

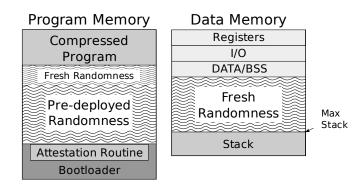

|   | 4.5  |          |                |                                                  | 76       |

|   |      | 4.5.1    |                |                                                  | 76       |

|   |      |          | •              |                                                  | 76       |

|   |      |          |                | e ,                                              | 77       |

|   |      |          |                | •                                                | 79       |

|   |      | 4.5.2    |                | 5                                                | 80       |

|   |      | 4.5.3    |                | 1                                                | 80       |

|   | 4.6  |          | -              |                                                  | 81       |

|   |      | concie   |                |                                                  | 01       |

| 5 | Prev | ention:  | Instruction    | -Based Memory Access Control                     | 83       |

|   | 5.1  | Introdu  | iction         |                                                  | 83       |

|   |      | 5.1.1    | Contributio    | ns                                               | 84       |

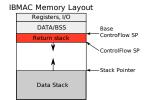

|   | 5.2  | Instruc  | tion-Based N   | Memory Access Control for Control Flow Integrity | 84       |

|   |      | 5.2.1    | Overview o     | f our solution                                   | 84       |

|   |      | 5.2.2    |                |                                                  | 85       |

|   |      | 5.2.3    | Instruction-   | Based Memory Access Control                      | 86       |

|   |      | 5.2.4    |                | •                                                | 87       |

|   | 5.3  | Impler   | -              |                                                  | 87       |

|   |      | 5.3.1    |                |                                                  | 87       |

|   |      |          | -              |                                                  | 88       |

|   |      |          |                | 1                                                | 88       |

|   |      |          |                | 1                                                | 88       |

|   |      |          |                | 1                                                | 89       |

|   |      |          |                | 8                                                | 89       |

|   |      | 5.3.2    | Evaluation     |                                                  | 91       |

|   |      | 5.3.3    |                |                                                  | 91       |

|   | 5.4  |          |                |                                                  | 93       |

|   | 5.4  | 5.4.1    |                |                                                  | 93<br>93 |

|   | 5.5  |          | 1              | . 1                                              | 93<br>94 |

|   | 5.5  | concie   |                |                                                  | <i>,</i> |

| 6 | Con  | clusions | and Future     | Directions                                       | 97       |

|   | 6.1  | Object   | ives of the th | sis                                              | 97       |

|   | 6.2  | Overvi   | ew of the the  | esis                                             | 97       |

|   | 6.3  | Future   | directions     |                                                  | 98       |

|   |      | 6.3.1    | Attack tech    | niques                                           | 98       |

|   |      | 6.3.2    |                | -                                                | 99       |

|   |      | 6.3.3    |                | -                                                | 99       |

|   |      |          |                | •                                                |          |

| A | Exte | ended French abstr  | ract                                                    | 109 |

|---|------|---------------------|---------------------------------------------------------|-----|

|   | A.1  | Introduction        |                                                         | 109 |

|   |      | A.1.1 Contexte      | de ce travail                                           | 109 |

|   |      | A.1.2 Contributi    | ons                                                     | 111 |

|   | A.2  | Attaque : Injection | n de Code sur Architectures Harvard                     | 112 |

|   |      |                     | ation de code par logiciel                              |     |

|   |      |                     | Les techniques existantes d'attestation de code         |     |

|   |      | A.3.0.2             | Deux attaques génériques                                | 114 |

|   |      |                     | Attaques sur protocoles d'attestation de code basés sur |     |

|   |      |                     | le temps de calcul                                      | 114 |

|   |      |                     | n : Attestation de toutes les mémoires                  |     |

|   | A.4  | Protection : Le co  | ontrôle d'accès mémoire en fonction de l'instruction    |     |

|   |      | exécutée            |                                                         | 116 |

|   | A.5  |                     | rspectives                                              |     |

| B | Mod  | lified SWATT impl   | lementation and attack                                  | 117 |

## **List of Figures**

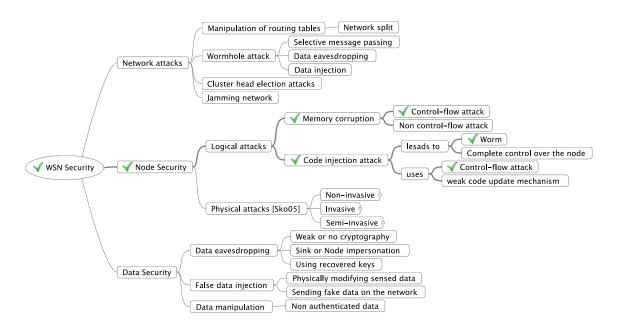

| 1.1  | Examples of attacks on Wireless Sensor Networks.                                  | 20 |

|------|-----------------------------------------------------------------------------------|----|

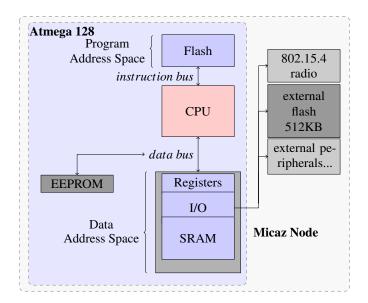

| 2.1  | Micaz memory                                                                      | 24 |

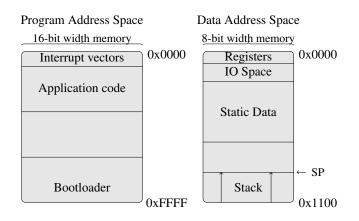

| 2.2  | Atmega 128 program and data memory                                                | 25 |

| 2.3  | Memory layout of a MSP430 micro-controller.                                       | 27 |

| 2.4  | Simple string based buffer overflow vulnerability                                 | 29 |

| 2.5  | Memory layout after buffer overflow                                               | 29 |

| 2.6  | Basic function call with call and return instructions                             | 29 |

| 2.7  | Normal function frame layout after a function call.                               | 30 |

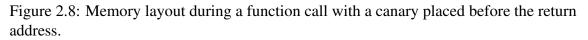

| 2.8  | Memory layout with canary                                                         | 34 |

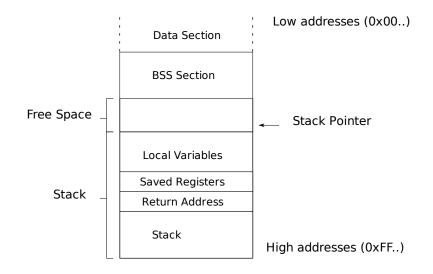

| 2.9  | Memory layout before a stack overflow                                             | 39 |

| 2.10 | Memory layout during a stack overflow                                             | 39 |

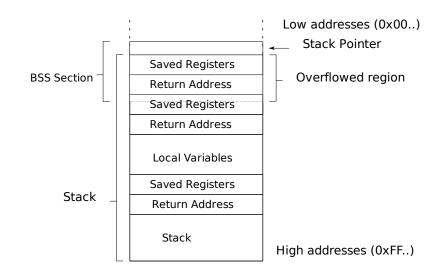

| 2.11 | Basic attestation challenge response protocol                                     | 41 |

|      |                                                                                   |    |

| 3.1  | Sample buffer management vulnerability.                                           | 47 |

| 3.2  | Payload of the injection packet.                                                  | 48 |

| 3.3  | Example buffer overflow                                                           | 48 |

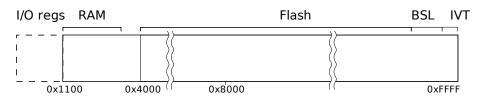

| 3.4  | Memory layout details of an Atmega128                                             | 50 |

| 3.5  | Ideal <i>Injection</i> meta-gadget.                                               | 51 |

| 3.6  | Real Injection meta-gadget.                                                       | 52 |

| 3.7  | <i>Reprogramming</i> meta-gadget                                                  | 55 |

| 3.8  | Payload of the <i>Reprogramming</i> packet                                        | 56 |

| 3.9  | Length of the shortest payloads found for the <i>Injection</i> meta-gadget        | 57 |

| 3.10 | Structure used to build the fake stack. The total size is 305 bytes out of        |    |

|      | which up to 256 bytes are used for the malware, 16 for the meta-gadget            |    |

|      | parameters. The remaining bytes are padding, that do not need to be injected.     | 58 |

| 3.11 | A memory cleanup procedure for TinyOS. The attribute keyword indicates            |    |

|      | that this function should be called during the system reinitialization            | 61 |

| 4.1  | Overview of memories on a MicaZ node; the EEPROM and external                     |    |

| 4.1  | memories are accessed from the I/O Registers.                                     | 65 |

| 4.2  |                                                                                   | 67 |

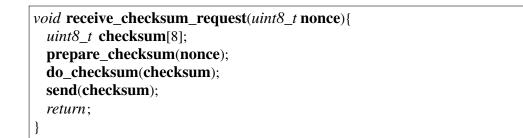

| 4.3  | Example of attestation function.                                                  | 67 |

| 4.4  | Timing of different attacks. The timings collected on SWATT with 128              | 07 |

| 4.4  | KBytes were performed with the same number of cycles that the original            |    |

|      | SWATT. On 128 KBytes the number of SWATT cycles should be increased,              |    |

|      | according to the <i>Coupon's Collector Problem</i> ; we have not done it in order |    |

|      | to have easily comparable values.                                                 | 68 |

|      |                                                                                   | 00 |

| 4.5                      | Compression Attack.                                                                                                                                                                                                                                                                                        | 69                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.6                      | Additional instructions of the memory shadowing attack; r31 holds high byte of random address, (Z is a 16-bit register and an alias to the 8-bit                                                                                                                                                           |                   |

| 4.7                      | registers r30 and r31)                                                                                                                                                                                                                                                                                     | 73                |

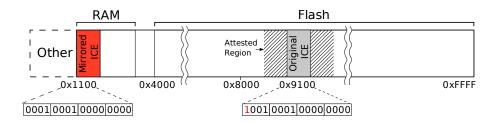

| 4.8                      | checksum, the attacker could store the modified attestation code there While the legitimate ICE routine is stored at address 0x9100, a malicious copy of the routine is stored at address 0x1100. These two addresses differ only in their most significant bit allowing the attacker to run the malicious | 73                |

| 4.9                      | copy of ICE and still pass attestation                                                                                                                                                                                                                                                                     | 75<br>79          |

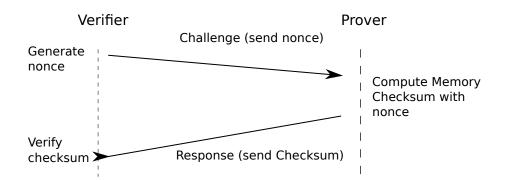

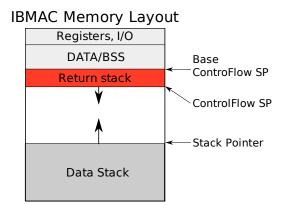

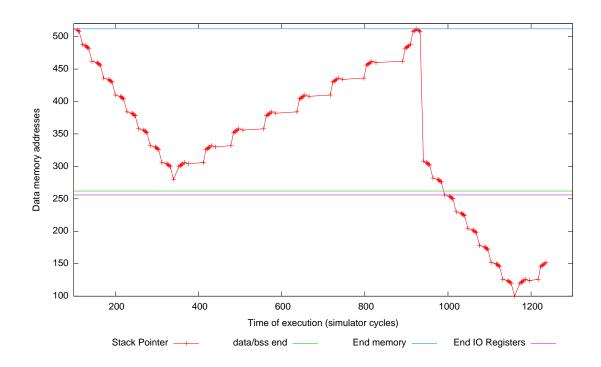

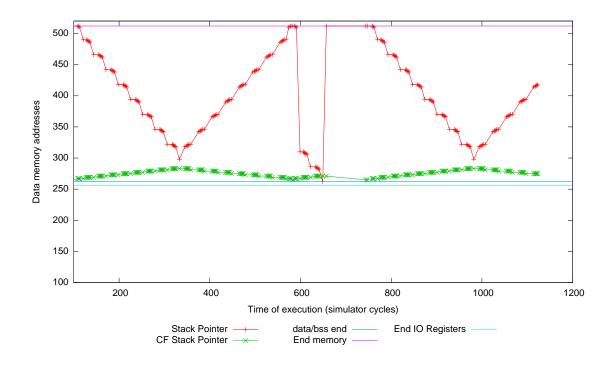

| 5.1<br>5.2               | Traditional stack layout                                                                                                                                                                                                                                                                                   | 85                |

| 5.3<br>5.4               | register that needs to be initialized in order to support IBMAC Example of a program that cause the stack to overflow                                                                                                                                                                                      | 86<br>90          |

| 5.5                      | data/BSS section and later on the I/O register memory area Execution <i>with</i> IBMAC enabled. When the return stack and the data stack collide (right after cycle 600), the execution of the program is aborted and restarted. This avoids memory corruption                                             | 92<br>92          |

| A.1<br>A.2<br>A.3<br>A.4 | Architecture mémoire d'un noeud de type MicaZ                                                                                                                                                                                                                                                              | 111<br>114<br>115 |

| B.1                      | Original SWATT implementation on AVR micro-controller. In the original paper, at the $6^{th}$ line the instruction is <i>st x</i> , <i>r16</i> . <i>r</i> 16 is never affected and <i>r</i> 30 holds the value to swap.                                                                                    | 117               |

| B.2                      | Malicious implementation of SWATT on a AVR micro-controller; main<br>loop is 2 cycles longer. This is possible because commutative operators are<br>used in the checksum computation (operator and and exclusive or).                                                                                      | 118               |

## **List of Tables**

| 2.1<br>2.2 | Mica motes family                                                                                                                                                                                                                                                                                    |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.1<br>4.2 | Compression Results                                                                                                                                                                                                                                                                                  |  |

| 5.1        | New register allocation for the additional registers. Note that the address chosen for the Atmega103 are registers that are already used in the real Atmega103, on our implementation the devices were not implemented so the registers were free. The registers allocation chosen for the Atmega128 |  |

| 5.2        | are unused registers in the original Atmega128L.                                                                                                                                                                                                                                                     |  |

## **Chapter 1**

## Introduction

### Contents

| 1.1 | Conte  | xt of this work              |

|-----|--------|------------------------------|

|     | 1.1.1  | Constrained embedded systems |

|     | 1.1.2  | Wireless Sensor Networks     |

|     | 1.1.3  | Embedded systems security 19 |

| 1.2 | Proble | em Statement 19              |

|     | 1.2.1  | Overview of possible attacks |

|     | 1.2.2  | Software attacks             |

| 1.3 | Contr  | ibutions                     |

| 1.4 | Orgar  | nisation of the thesis       |

The context of this thesis is the security of low-end embedded systems, such as wireless sensor networks. Low-end embedded systems have been present for decades and have computing capabilities comparable to that of personal computers of 20 or 30 years ago <sup>1</sup>. Section 1.1.1 introduces low-end embedded systems. In the last decade, Wireless Sensors Networks, large networks of wirelessly connected low-end devices, have been the center of a tremendous amount of research, both academic and industrial. These systems, that are introduced in Section 1.1.2, are envisioned to be used at large scale in fields such as factory control and automation or smart grid. Their pervasive presence as well as their pervasive networks more important than ever. Moreover, those systems can handle personal data, such as medical information, and protecting this information is crucial, Section 1.1.3 introduces those security challenges.

## 1.1 Context of this work

## 1.1.1 Constrained embedded systems

The "*embedded system*" term covers a very large number of different devices. By usual agreement an embedded system is a device that is dedicated to a specific purpose and

<sup>&</sup>lt;sup>1</sup>for example the Apple 1 or the Commodore 64.

has no or an uncommon user interface. To some extent all computing devices except desktop and server computers could defined as embedded systems. In this work, we focus on low-end embedded systems with strong constraints of available memory, computing capabilities energy and cost. Those devices usually rely on a 8 or 16-bit microcontroller. Microcontrollers embeds on one silicon die both the core (or processor) as well as memories and peripheral devices such as bus interfaces (serial, SPI, UART...), signal converters (Digital to analog and analog to digital converters), and possibly network devices (Ethernet, IEEE 802.15.4,etc.. ). This high level of integration allows to keep a very low production cost of the final device. Most of what is needed for the system is present in one chip. This simplifies the production of the device and therefore reduce its cost. One of the most expensive part of a micro-controller is the memory. The SRAM memory can occupy a large portion of the final silicon surface. Therefore, this is usually one of the main constraints. For example low-end micro-controllers have typically between 4 to 10 KBytes of SRAM memory.

## **1.1.2** Wireless Sensor Networks

Wireless Sensors Networks (WSN) are constrained embedded devices that forms a network using radio communications. WSN nodes are deployed in large networks of, for example, thousands of units. Each node can have sensing capabilities.

Even tough, it is still expensive to deploy large scale wireless sensor networks, it is foreseen that, thanks to the Moore's law, larger networks will become affordable at some point in the future. Following this law, at constant hardware capabilities of each node, devices will constantly become cheaper. Therefore, the number of nodes that forms a WSN could be increased at constant cost, i.e., large wireless sensor networks will become affordable.

The sensing capabilities of a WSN node can be used to monitor the current hydrometry or temperature. WSN can be used for surveillance of a restricted area to detect, for example, the presence of an intruder. His presence could be reported immediately to an operator thanks to ad-hoc communications in the wireless network. Another example of wireless sensor network is to sense environment for polluting chemicals.

They are envisioned to be used for critical applications and/or in hostile environments (military applications, security control or natural risks prevention ...) where WSN security is a major concern. Other applications include new smart meters, that would make possible to perform fine load balancing on power distribution grid. In such a scenario, the device or its power plug would embed a small WSN device that could wirelessly report its measures and requirements to the power meter. On the other direction, the power meter could be noticed by the power grid administrator (or more likely software) to reduce its power consumption in order to offload the power grid. In such a case the power meter could inform devices such as fridges or cooling systems to reduce its power consumption.

One of the major challenge introduced by WSN is the design of dependable, secure, and power efficients protocols and applications on such low-end and possibly unreliable hardware.

### **1.1.3 Embedded systems security**

Embedded systems are commonly used for safety critical applications and can be deployed in hostile environments. They are often left unattended for long periods or are just physically inaccessible. Hardware attacks specific to embedded systems and related countermeasures have been largely studied. Different types of physical attacks are possible; non-invasive physical attacks, semi-invasive attacks and invasive attacks.

Non-invasive attacks monitor the behavior of a device (current consumption, electromagnetic radiation, timing attack) in order to understand the ongoing computations. Information leakage from power consumption allows Simple Power Analysis (SPA) or Differential Power Analysis (DPA) to be performed. Those attacks can lead to the recovery of the cryptographic key used internally by the embedded system.

In a semi-invasive attack [Sko05] the embedded system is put under unusual conditions such as generating faults which simulates short power failures (glitching attacks), or unusual environment (e.g. using a laser to generate faults).

Finally, invasive attacks are destructive; the package of the microprocessor is removed. The microprocessor can then be analyzed under a microscope, signal on buses can be monitored using probes (thin needles are drooped on a bus and connected to an analyzer). Focused Ion Beam (FIB) devices allows an attacker to modify the processor logic, for example removing or adding a wire on the processor. Those attacks are typically performed on smart-cards, e.g. to recover a secret key.

Countermeasures against those physical attacks, have been developed, mainly for the smart card industry, that make all those attacks impossible or more difficult to perform. For example, the layout of the chips are randomized (glue logic layouts), tamper resistance is increased with additional layers of metal or insulators to protect the chip. The processors and algorithms are designed to leak less information (electromagnetic signals or non constant timings) that would allow DPA or SPA to be performed.

Comparatively, few work have been published in the context of purely software attacks and their counter-measures on embedded systems. While software-only attacks are the main attack vector on commodity systems. However, as the connectivity of these devices with the outside world increases, the possibility that these devices might be remotely subverted increases as well.

Computer systems are subject to remote attacks that aim at controlling their software behavior, which often require control flow manipulation. Such attacks, that we refer to as *Control Flow Attacks*, have been one of the main attack vectors to computer systems in recent years. Despite their limited computation capabilities low-end embedded systems are not an exception to this, several attacks have been recently shown to be practical and feasible on them [Goo07].

## **1.2 Problem Statement**

Wireless sensor network security is many-fold, there are various ways to attack them. It is commonly assumed that wireless sensor networks are based on non tamper resistant devices, i.e. an attacker can easily collect a few nodes to analyze or modify them. However, as the network is large, possibly made of hundreds or thousands of devices, an attacker cannot tamper with all the devices. This is a basic assumption in security protocols designed for wireless sensor networks. An attacker can chose to attack the network, the

Figure 1.1: Examples of attacks on Wireless Sensor Networks.

data or directly the nodes. We discuss the possible attack vectors in the next sections.

### **1.2.1** Overview of possible attacks

**Network based attacks** When an attacker targets the network he will usually rely on a few subverted nodes to mount routing attacks [KW03]. Examples of such attacks are wormholes or network partition attacks.

In a *wormhole attack* the attacker controls at least two nodes, which are located in two different places of the network. Moreover, those nodes are modified and connected together using an out of band mechanism. The malicious nodes are then able to communicate with their neighbors and with the other remote malicious node.

The attack consists in forwarding messages using the out of band mechanism. One of the very common objective of routing protocols is to build the shortest path between nodes. As the wormhole attack builds a very efficient path between nodes many routes will include this malicious path. The consequences of this attack is to give an advantage to the attacker, an important fraction of the messages are routed through his malicious nodes. He can use this advantage for many attacks, for example, selectively dropping messages or eavesdropping data.

In a *Sybil attack* [Dou02] a malicious device impersonates several identities in order to act as several devices. In a WSN [NSSP04] a device could steal identities or reuse stolen identities, this allows such a device to e.g. have more weight in a election based protocol or to disrupt routing protocols [KW03]. This attack could as well impact other important features in WSN such as data aggregation, resources allocation or detection of misbehavior.

Other attacks are possible for an attacker that can control and manipulate the routing protocol, for example using packet injection or jamming. This could be used to selectively drop packets (e.g. an alert packet, a command), split the network in two logically separate parts redirect measurements to an attacker controlled node..

Attacks on the data collected Without appropriate authentication of the nodes an attacker can impersonate a node to send fake data. An attacker not part of the network can tamper with the data. While there exists many Data authentication is a difficult problem in WSN, therefore data tempering by a malicious node is a difficult problem. Secure data aggregation protocols have been proposed to solve those issues. In a physical intrusion detection alarm system, the authority using the system would be willing that the alarms reported are secret, i.e. the messages passing would not to acknowledge the detection of the intruder. This for example would allows the authority to caught the intruder in the act.

Attacks on the nodes themselves The third approach to attack a wireless sensor network is to target the nodes themselves. Some attacks are specific to WSN such as denial of sleep attacks, where an attacker performs actions such as sending data packets, for example with an invalid cryptographic signature in order to deplete the battery of the device by preventing it to go into sleep mode. In the following we focus mainly on Software attacks.

## 1.2.2 Software attacks

Software attacks have been known and used for more than 20 years on general purpose computers (see Section 2.2.1), on the other hand software attacks have not been considered on Wireless Sensor Networks. Given the high impact that control flow attack had on commodity systems, many countermeasures have been proposed to defend against those attacks, such as: binary randomization [KJB<sup>+</sup>06], memory layout randomization [The03b, The03a], stack canaries [CPM<sup>+</sup>98], tainting of suspect data [SLZD04] enforcing pages to be writable or executable [AMD, The03a], Control Flow Integrity enforcement [ABUEL05]. However, most of those countermeasures are demanding in terms of computation capabilities, memory usage and often rely on hardware that is unavailable to simple micro-controllers, such as a Memory Management Unit (MMU) or execution rings. Moreover, they mostly use software solutions as hardware modifications (for example on the *x*86 architecture) are difficult and likely to cause problems with legacy applications.

Most of those attacks and countermeasures have not been well studied in the context of wireless sensor networks. The goal of this thesis is therefore to study the feasibility of software attacks on WSN architectures and the possible counter-measures.

## **1.3 Contributions**

The contributions of this thesis are many-fold:

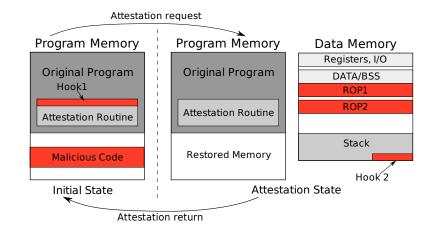

- it demonstrates the feasibility of permanent code injection attacks in embedded systems relying on an Harvard architecture. Such architectures were largely believed to be immune to code injection attacks. We further discuss how an attacker could use this attack to produce a worm that would spread over a wireless sensor network.

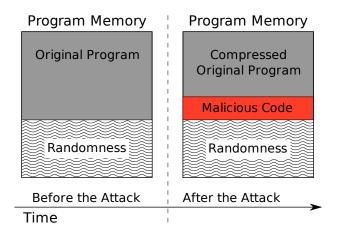

- it shows weaknesses of previous software-based attestation protocols. We introduce two generic attacks. The first generic attack compresses the original program in order to free memory for malicious code. The malicious code can then perform on the fly decompression of the original program to pass the attestation protocol. The

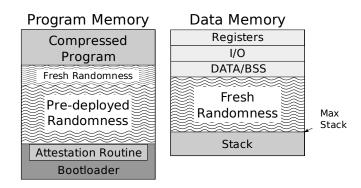

second generic attack relies on a return-oriented rootkit that hides malicious code in non executable memories to avoid detection. We then describe some specific attacks against previously proposed attestation protocols, ultimately showing the difficulty of software-based attestation design. Furthermore, we propose a software-based attestation protocol for WSNs that prevents those attacks.

it introduces a simple but effective hardware protection against control flow attacks for the AVR family of micro-controllers. The defense relies on using a protected separate stack for storing return addresses. The technique has been implemented and validated on both a simulator and an AVR core on a FPGA (i.e. a soft-core). This implementation shows the modest overhead required in terms of logical elements units. This approach does only introduce negligible run-time overhead and is backward compatible with all major software functionality. Besides defending against attacks this stack layout can also be very helpful for software reliability to prevent stack overflow.

## **1.4 Organisation of the thesis**

This thesis presents work that has been done during my PhD concerning software security of embedded systems. This introduction has presented the context, motivations and contributions of the work of this thesis. The next chapter describes in more details the common architectures of Wireless Sensor devices as well as usual software attacks and countermeasures.

Chapter 3 shows that Harvard architecture devices are not immune to code injection attacks. A practical attack is described and its consequences are discussed.

Chapter 4 focuses on how to remotely detect device compromises without dedicated hardware. The objective is, for example, to be able to detect an attack such as the code injection attack of Chapter 3 but also modifications of the program that could be performed by other means. To this purpose, we review existing protocols for remote software attestation and we describe their limitations. Finally, we present an approach which is resistant to the attacks we described against previous protocols.

Finally, Chapter 5 introduces a modification to the memory architecture of a microcontroller that would prevent most of the attacks presented in the previous chapters, such as exploitation of stack-based buffer overflows and *return-oriented programming*. We describe its implementation both in a simulator and a soft-core on a FPGA.

Chapter 6 concludes and gives future directions of research. An extended abstract in French is given in Appendix A.

## Chapter 2

## **State of The Art**

#### Contents

| 2.1 | Overvi | ew of common WSN device architectures                    |

|-----|--------|----------------------------------------------------------|

|     | 2.1.1  | Harvard architecture: the AVR                            |

|     | 2.1.2  | Von Neumann architecture: TI MSP430                      |

| 2.2 |        | are attacks and counter-measures on general purpose com- |

|     | 2.2.1  | Software attacks on general purpose computers            |

|     | 2.2.2  | Mitigation techniques on general purpose computers 33    |

| 2.3 | Softwa | re attacks and detection on WSN nodes                    |

|     | 2.3.1  | Attacks                                                  |

|     | 2.3.2  | Software-based attestation                               |

| 2.4 | Conclu | usion                                                    |

This chapter first introduce two wireless sensor network architectures, one relying on the MSP430 micro-controller and another relying on an AVR micro-controller. Those two devices are using radically different memory architectures. The AVR has an Harvard memory architecture while the MSP430 has a Von Neumann memory architecture.

We then present common attacks vectors on general purpose computers, such as stackbased buffer overflows, as well as the different steps required by an attacker to turn them into successful attacks. We then present the different mitigation techniques either present in operating systems or as academic proposals.

Finally we discuss the state of the art of the software attacks and defenses for wireless sensor networks.

## 2.1 Overview of common WSN device architectures

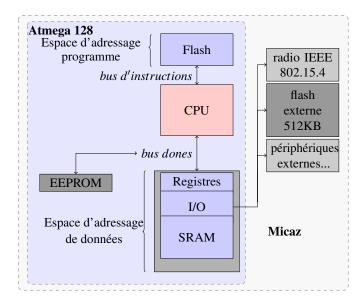

### 2.1.1 A Harvard-based architecture micro-controller: Atmel AVR

Some of the most common devices for Wireless Sensor Networks experimentation are the family of Mica motes. The Micaz device [Mic04] is one of the most common platform for WSNs. Micaz is based on an Atmel AVR Atmega 128 8-bit micro-controller [ATM]

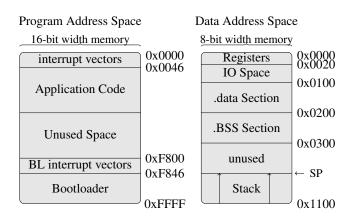

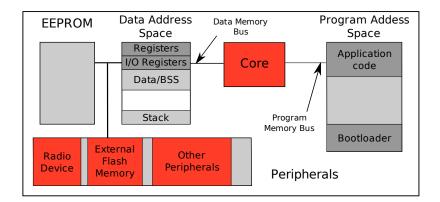

Figure 2.1: Micaz memory architecture putting in evidence the physical separation of memory areas, on top of the figure we can see the flash memory which contains the program instructions.

clocked at a frequency of 8MHz and an IEEE 802.15.4 [IEE06] compatible radio. Many variants of this device exists, we list some of them in Table 2.1.

## 2.1.1.1 The AVR architecture

The Atmel Atmega 128 [ATM] is a Harvard architecture micro-controller. In such microcontrollers, program and data memories are physically separated. The CPU can load instructions only from program memory and can only write in data memory. Furthermore, the program counter can only access program memory. As a result, data memory can not be executed. A true Harvard architecture completely prevents remote modification of program memory. Modification requires physical access to the memory. As this is impractical, true Harvard-based micro-controllers are rarely used in practice. Most of Harvard-based micro-controllers are actually using a *modified Harvard architecture*. In such architecture, the program can be modified under some particular circumstances.

For example, the AVR assembly language has dedicated instructions ( "Load from Program Memory" (LPM) and "Store to Program Memory" (SPM) ) to copy bytes from/to program memory to/from data memory. These instructions are only operational from the bootloader code section (see Section 2.1.1.3). They are used to load initialization values from program memory to data section, and to store large static arrays (such as key material or precomputed table) in program memory, without wasting precious SRAM memory. Furthermore, as shown in Section 2.1.1.3, the SPM instruction is used to remotely configure the Micaz node with a new application.

### 2.1.1.2 Memory architecture

As shown on Figure 2.1, the Micaz Wireless sensor node relies on an Atmega 128 microcontroller which has three internal memories. The Micaz embeds an external memory, a flash chip, on the Micaz board.

Figure 2.2: Typical memory organization on an Atmel Atmega 128. Program memory addresses are addressed either as 16 bits words or as bytes depending on the context.

- The internal flash (or program memory), is where program instructions are stored. The microprocessor can only execute code from this area. As instructions are two bytes or four bytes long, program memory is addressed as two-byte words, i.e., 128 KBytes of program memory are addressable. The internal flash memory is usually split into two main sections: application and bootloader sections. This flash memory can be programmed either by a physical connection to the micro-controller or by self-reprogramming. Self-reprogramming is only possible from the bootloader section. Further details on the bootloader and self-reprogramming can be found in Section 2.1.1.3.

- Data memory address space is addressable with regular instructions. It is used for different purposes. As illustrated in Figure 2.2, it contains the registers, the Input Output area, where peripherals and control registers are mapped, and 4 KBytes of physical SRAM.

Since the micro-controller does not use any Memory Management Unit (MMU), no address verification is performed before a memory access. As a result, the whole data address space (including registers and I/O) are directly addressable.

- The EEPROM memory is mapped to its own address space and can be accessed via the dedicated IO registers. It therefore can not be used as a regular memory. Since this memory area is not erased during reprogramming or power cycling of the CPU, it is mostly used for permanent configuration data.

- The Micaz platform has an external flash memory which is used for persistent data storage. This memory is accessed as an external device from a serial bus. It is not accessible as a regular memory and is typically used to store sensed data or program images.

### 2.1.1.3 The bootloader

A sensor node is typically configured with a monolithic piece of code before deployment. This code implements the actions that the sensor is required to perform (for example, collecting and aggregating data). However, there are many situations where this code needs to be updated or changed after deployment. For example, a node can have several modes

2.1. OVERVIEW OF COMMON WSN DEVICE ARCHITECTURES

of operation and switch from one to another. The size of program memory being limited, it is often impossible to store all program images in program memory. Furthermore, if a software bug or vulnerability is found, a code update is required. If a node cannot be reprogrammed, it becomes unusable. Since it is highly impractical (and often impossible) to collect all deployed nodes and physically reprogram them, a code update mechanism is provided by most applications. We argue that such a mechanism is a strong requirement for the reliably and survivability of a large WSN. On an Atmega128 node, the reprogramming task is performed by the bootloader, which is a piece of code that, upon a remote request, can change the program image being ran on a node.

External flash memory is often used to store several program images. When the application is solicited to reprogram a node with a given image, it configures the EEPROM with the image identifier and reboots the sensor. The bootloader then copies the requested image from external flash memory to program memory. The node then boots on the new program image.

On a Micaz node, the bootloader copies the selected image from external flash memory to the RAM memory in 256-byte pages. It then copies these pages to program memory using the dedicated SPM instruction. Note that only the bootloader can use the SPM instruction to copy pages to program memory. Different images can be configured statically, i.e., before deployment, to store several program images. Alternatively, these images can be uploaded remotely using a code update protocol such as TinyOS's Deluge [HC04].

| device                     | micro-controller | Frequency | SRAM | flash | Storage | radio device  |

|----------------------------|------------------|-----------|------|-------|---------|---------------|

|                            | Atmel            | (MHz)     | (KB) | (KB)  | (KB)    |               |

| Rene [GKW <sup>+</sup> 02] | 90LS8035         | 4         | 0,5  | 8     | 256     | RFM TR1000    |

| Mica [Sto05]               | Atmega 103       | 4         | 8    | 128   | 512     | RFM TR1000    |

| Mica2 [Mic]                | Atmega 128L      | 8         | 4    | 128   | 512     | CC1000        |

| MicaZ [Mic04]              | Atmega 128L      | 8         | 4    | 128   | 512     | CC2420        |

| Fleck[HCSO09]              | Atmega 128L      | 8         | 4    | 128   | 8192    | Nordic nRF903 |

#### 2.1.1.4 Wireless Sensor Nodes based on the AVR architecture

Table 2.1: Mica motes family

## 2.1.2 A Von Neumann Architecture Micro-Controller : The Texas Instruments MSP430

#### 2.1.2.1 The MSP430 architecture

The Texas Instruments MSP430 [Tex] is a family of micro-controllers present in a very large number of embedded systems. It features a very low sleep power consumption. Therefore, it is a good choice for building Wireless Sensor Networks devices. Table 2.2 presents some examples of Wireless Sensor nodes built around a MSP430 micro-controller.

As with the AVR architecture the MSP430 is a micro-controller that is widely used across the embedded systems, it is present in a large range of applications. For example, the Advanced Metering Infrastructure (AMI) integrates microcontrollers into each electric power meter of a city, and many devices in cars rely upon a microcontroller.

Figure 2.3: Memory layout of a MSP430 micro-controller.

### 2.1.2.2 Memory architecture

On the opposite of the Atmel AVR architecture the Texas Instruments MSP430 has a Von Neumann memory architecture. It's memory is organized within one address space, where both executable code and data are located (Figure 2.3). This is by far the most common memory architecture, present in most processors used in general purpose computers (e.g. Intel x86 or x86\_64 architectures, MIPS, ARM, SPARC...). One direct security implication is that, if no specific countermeasures are in place, all memories are executable. Therefore, classical stack-based buffer overflows that inject code in the stack are possible, such an example has been presented in [Goo08, Goo07].

### 2.1.2.3 The Bootloader

The MSP430 has the particularity to embed a fixed *Boot Strap Loader* (BSL) [Sch06]. This BSL resides in mask ROM, at a fixed position and is present in all chips, it is programmed during manufacture (during mask fabrication). It is often used to allow for write-only updates without exposing internal memory to a casual attacker. Each firmware image contains a password, and without that password little more is allowed by the BSL than erasing all of memory. In some applications such as in TinyOS remote reprogramming protocol *Deluge* [HC04] an extra bootloader is installed in Flash memory that includes application dependent functionality. For example the TinyOS bootloader for the MSP430 is able to reprogram the device from a program image stored in a storage device (an external Flash memory in the case of the TelosB mote). Together with a code distribution protocol, this allows remote reprogramming of wireless sensor network devices.

#### 2.1.2.4 Wireless Sensor Nodes based on the MSP430 architecture

| device       | micro-controller | sram memory | flash | ext Flash | radio          |

|--------------|------------------|-------------|-------|-----------|----------------|

| Tmote sky    | MSP430F1611      | 10KB        | 48KB  | 1MB       | CC2420         |

| TinyNode 184 | MSP430F241       | 8KB         | 92KB  | 512kB     | 868 / 915MHz   |

|              |                  |             |       |           | Semtech SX1211 |

| TelosB       | MSP430F1611      | 10KB        | 48KB  | 1MB       | CC2420         |

| Table 2.2: | Motes families based on the TI MSP430 micro-controller |

|------------|--------------------------------------------------------|

|------------|--------------------------------------------------------|

# 2.2 Software attacks and counter-measures on general purpose computers

## 2.2.1 Software attacks on general purpose computers

### 2.2.1.1 Code injection attacks

Code injection attacks are common on general purpose computers and count among the most dangerous attacks on a system. If an attacker is able to inject arbitrary code in a system, he is able to perform any possible actions at the current privilege level. Those attacks rely for example on:

- using social engineering to trick the user into executing a malicious program,

- opening a document that embed malicious scripts,

- abusing a update mechanism [CSBH08],

- improper checks on user supplied data,

- abusing of software vulnerabilities.

In this section we focus on the abuse of software vulnerabilities. One of the first widespread use of such attacks is the Morris worm (also known as *the Internet worm*) [Spa89b, See89]. The Morris worm spread on the Internet during winter 1988. The Internet was composed of only a few thousands nodes at that time but the spread of the worm was very fast and it disrupted an important part of the network. The worm was active for a few days before being stopped [Spa89a]. The analysis of the worm showed that, among several infection techniques used, it performed a stack-based buffer overflow that exploited a vulnerability in the finger daemon in order to inject code on the stack. This injected code was then executed from the stack and launched a shell, which gave full control of the computer to the worm.

In this section we describe common techniques used for code injection attacks that abuse software vulnerabilities. In Section 2.2.2 we describe common counter-measures as well as techniques used for detection of such attacks.

**Buffer overflow** A buffer overflow condition (also known as buffer overrun) occurs when data is written to a memory allocated region which is not large enough to contain the data. If proper boundaries check are not in place to prevent the overflow, memory regions contiguous to the overflowed buffer will be corrupted. The possibility and consequences of exploiting the overflow depends on the location of the overflowed buffer.

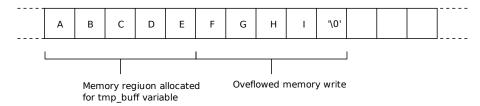

There exists a set of very well known functions or coding techniques [Sea08] that are unsafe and often leads to buffer overflows. For example, string manipulations that rely on the presence of a NULL byte at the end of the string are subject to buffer overflow. Such standard functions do not check the length of the string but instead rely on the NULL byte to detect the end of the character chain. Figure 2.4 shows a code that performs a string copy using the unsafe *strcpy* function. The data copy ends only when a NULL byte is found in the source string however the source string is longer than the allocated destination variable. Figure 2.5 shows the resulting memory layout with the characters *FGHI* written

// ...

char src="ABCDEFGHI";

char tmp\_buff[5];

// ..

strcpy(tmp\_buff,src);

// perform some action on backup string tmp\_buff

// ...

Figure 2.4: Simple string based buffer overflow vulnerability.

Figure 2.5: Memory layout after the buffer overflow presented in Figure 2.4.

after the end of the dedicated memory region for the *tmp\_buff* variable. On a general purpose computer if this memory region is not in a mapped memory page this will result in a segmentation fault error. However, if the overflow remains in a valid memory page it will likely overwrite another variable.

The position in memory of the overflowed buffer is crucial to the ability of an attacker to exploit it for malicious purposes. In the following sections we show how this can be used to perform malicious actions.

#### Stack-based buffer overflow: Control flow manipulation using a buffer overflow

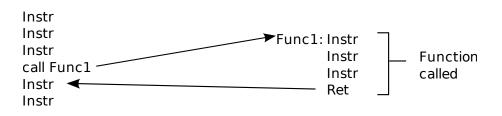

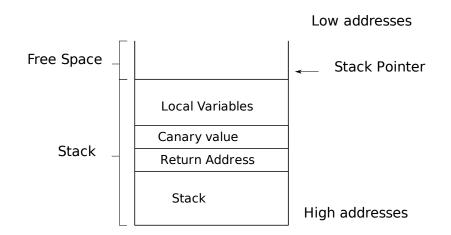

Functions and procedures are basic building blocks of programming languages, they embed code that implement an action in an independent block. Functions are called with a *call* instruction that diverts the control flow to the top of the function code. Upon completion the execution is returned to the caller with a *return* or *ret* instruction (Figure 2.6). During the *call* instruction the address to return to (i.e. the address of the instruction following the call instruction) is saved on the stack, this same address is retrieved from the stack by the return instruction.

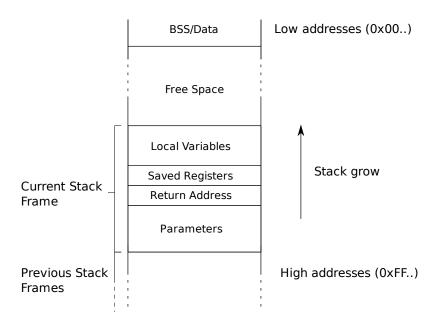

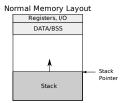

On most microprocessors a unique stack is used to store control flow information as well as other data. Each *frame* of the stack usually contains the following data:

- saved return address of the caller;

- function variables and parameters;

Figure 2.6: Basic function call with call and return instructions

Figure 2.7: Normal function frame layout after a function call.

• saved register values, according to the specific Application Binary Interface (ABI).

Implementation details vary across different architectures, Figure 2.7 depicts a simple layout example for a portion of the stack. Control flow information, such as return addresses, are stored alongside other function data.

When a buffer overflow occurs on a buffer allocated on stack the attacker is able to overwrite part of the stack. One of the most interesting part of the stack for an attacker is the return address saved during a function call. This return address is used when the function executing ends (i.e. a return instruction will be executed) to move the program counter to the code where the function was called. However, if this return address was maliciously modified with a buffer overflow the attacker has gained full control over the program counter.

Buffer overflows that occurs on a variable not allocated on stack can also lead to control flow manipulation. A common example of such an attack is when a buffer allocated close to a function pointer is overflowed. With such an overflow the attacker can modify the value of the function pointer. Latter, when the function is called from this pointer the control flow will be redirected to the code of the choice of the attacker.

**Redirecting execution on stack** In it's most basic form a stack-based buffer overflow is used to inject instructions (i.e. the *payload* or *shellcode*) on the stack and redirect the control flow to those instructions by modifying the return address. This attack becomes more difficult when the attacker is unaware of the current stack pointer or address where the instructions were written. When this address is not accurately known the attacker either needs to guess the address, which can be very slow, or needs to use other techniques such as using a *NOP sledge* or finding *trampolines* [SD08].

A NOP sledge is a long sequence of instructions, that performs no operations, which is inserted before the actual injected instructions. When the attacker has an approximate guess of the position of his injected code, he is able to redirect execution to an address in the NOP sledge. The processor will then execute the NOP instructions until the actual payload is reached. Therefore, the attacker does need to know exactly the address where the payload has been written, only an approximate knowledge is enough to redirect execution in the *NOP sledge*.

Another common technique used to execute code on the stack is the use of *trampolines*. An attacker will locate an instruction such as *jmp esp* or *call esp* (Intel x86 assembly) that directly redirects execution to the stack. If such an instruction is found at a fixed address he will use this address to overwrite the return address on stack. This will lead to execute the trampoline which will in turn redirect execution on the payload stored in the stack.

#### 2.2.1.2 Malicious code execution without code injection

**Return to libc : redirection to existing functions** The previously described technique assumes that the stack (or other memory region writable by an attacker) is executable. However, this is not the case with modern operating systems that provides defenses against execution of code on any writable section (described in Section 2.2.2.2). This is also impossible to execute instructions from the stack on Harvard architecture processors as we will describe in Section 2.1.1.

Several techniques have been therefore developed to bypass these protection mechanisms. One of the first public technique was the *return to libc* (Also known as *returninto-libc*) attack [Sol97] where the attacker does not inject code to the stack anymore but instead executes a function present in the address space. As on UNIX systems the C library (libc) is loaded for most programs in order to use basic functions of the C library, it is convenient to use the libc as a target of the *return to libc* attack. Moreover, the C library contains interesting functions for an attacker, the most common function called in a *return to libc* are the *system* or the *exec* function.

The *return to libc* attack, when it uses a stack-based buffer overflow, usually consists in writing data to the stack and overwriting a return address on stack. This address is modified to point to a function, at a known location, which will be called when the exploited function returns. When this function is called it will look for parameters on the stack, and use the data that was previously written by the attacker during the buffer overflow. Therefore, the attacker is able to execute any function and pass parameters to it. The most commonly used functions are the exec or system functions, to which is passed an argument that spawns a shell or open a server socket on the system under attack. Using those functions, and being able to pass arbitrary parameters to it, it is easy to launch a shell or open a socket for latter connection. Subsequently the attacker can connect to this socket an obtain a prompt, he has full control over the system.

**Borrowed code chunks** As seen above, the *return to libc* technique works well when the functions called by the attacker do not need parameters or when the Application Binary Interface (ABI) requires parameters to be passed on the stack. However, if parameters needs to be passed in registers this attack can't work directly as the attacker's data is only present in the stack. This is the case in the 64-bit Intel architecture <sup>1</sup>. The *borrowed code chunks* [Kra05] technique was developed as an enhancement to the *return to libc* attack to load parameters to registers. The main idea is to craft a payload that will chain code present in the application address space (e.g. application code or libraries) to load proper

<sup>&</sup>lt;sup>1</sup>AMD64 or Intel x32\_64

values from the stack to registers. Once those values have been moved to registers the function can be executed (e.g. "returned to") with the parameters loaded in registers.

As the code chunks are carefully selected to contains a few instructions and terminate with a return instruction, it is possible to chain them. To chain those code chunks, the attacker needs to build a stack layout that contains the data that will be used by the code chunk (e.g. when a pop instruction is encountered) as well as the return addresses that points to the next code chunk. Therefore, by chaining the code chunks together it is possible to write an attack payload that perform more complex attacks.

**Return-Oriented Programming** The "return-into-libc" and code chunks borrowing attacks have been extended into a more generic attack. *Return-Oriented Programming* [Sha07, BRSS08, RBSS09] generalizes this technique and defeats systems that prevents execution of code in writable memory regions <sup>2</sup> by executing preexisting sequences of instructions to perform arbitrary computations. Group of instructions terminated by a *return* instruction, called *Gadgets*, are first located in the process address space. Gadgets are performing actions useful to the attacker (i.e., pop a value in stack to a register) and returns to another gadget. The objective of the attacker is to find a Turing complete gadget set. A Turing complete gadget set can be used to build a Turing machine and therefore the attacker can chain those gadgets by controlling the stack to perform arbitrary computations. While this was first demonstrated on the Intel x86 architecture, it was further demonstrated to be possible on the SPARC architecture. Once a Turing complete gadget set is available it is possible to build a compiler to automatically generate return-oriented programs [RBSS09, RH09].

### 2.2.1.3 Non buffer overflow-based software attacks

Many different techniques are used to launch software attacks. We previously detailed the techniques used during starting with a buffer overflow. This section describe other sources of control flow manipulations.

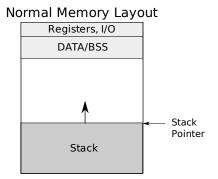

**Stack overflow** A *stack overflow* is an event that occurs when the stack usage grows until it reaches and overlaps with another section of memory. This is the definition we will use throughout this section and it must not be confused with *stack-based buffer overflow*. As seen in Section 2.2.1.1 the latter is the consequence of a vulnerable or malfunctioning program (e.g. improper boundary check) and the former is the consequence of an out-of-memory condition.

*Stack overflow* is an out of memory condition common in embedded systems with highly constrained memory availability. This, for example, means that the stack overflow can occur with a correct program or a program written in a type or memory safe language. When this happens on a general purpose computer the situation is detected thanks to guard pages that limits the stack growth. however, this is a limited defense as, in some cases, the guard page can be "jumped" over [Del05].

**Other sources of control flow manipulation** Any software vulnerability that can allow an attacker to write memory at arbitrary position can lead to a control flow attacks. With an arbitrary memory write an attacker can modify a return address or a function pointer to manipulate the control flow [tt01]. Improper string format usage in functions such as

<sup>&</sup>lt;sup>2</sup>such as the  $W \oplus X$  technique, this is introduced in more details in Section 2.2.2.2